導(dǎo)航

微信

頂部

news center

發(fā)布時(shí)間:2023-11-28 閱讀: 來源:管理員

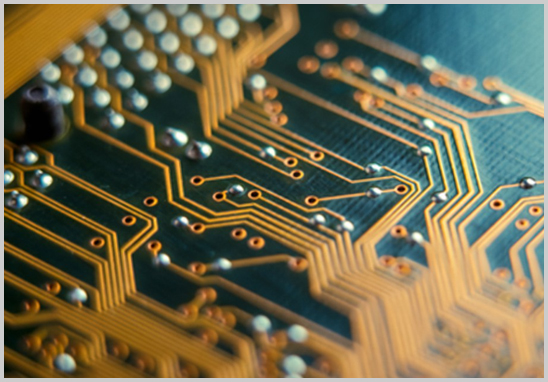

PCB設(shè)計(jì)中的走線布局是非常關(guān)鍵的步驟,它直接影響電路性能和 EMC(Electromagnetic Compatibility)特性。深圳宏力捷電子是專業(yè)PCB設(shè)計(jì)公司,可承接多層、高精密/BGA封裝以及盲孔/埋孔的PCB設(shè)計(jì)畫板服務(wù),客戶只需提供原理圖,我們可完成電路板布局、建立BOM表、搜尋供應(yīng)商及購料、樣品制作等服務(wù)。

1. 層次規(guī)劃: 在設(shè)計(jì)之前,規(guī)劃好 PCB 的層數(shù)。多層 PCB 可以提供更多的走線空間和地平面,有助于減小信號(hào)層間的串?dāng)_。

2. 信號(hào)分類: 對(duì)信號(hào)進(jìn)行分類,例如將模擬信號(hào)、數(shù)字信號(hào)和電源信號(hào)分開。不同類型的信號(hào)應(yīng)該盡可能分布在不同的層上,以減小干擾。

3. 地平面規(guī)劃: 使用連續(xù)的地平面可以降低信號(hào)層間的串?dāng)_,提高電路的抗干擾能力。地平面應(yīng)該盡可能覆蓋整個(gè) PCB,并避免斷開。

4. 差分對(duì): 對(duì)于差分信號(hào)(如 USB、HDMI、以太網(wǎng)等),要保持它們的差分對(duì)布線,以最小化串?dāng)_。差分對(duì)的兩個(gè)信號(hào)要盡可能靠近,且它們的路徑長度應(yīng)該盡量相等。

5. 阻抗匹配: 對(duì)于高頻信號(hào),要注意保持信號(hào)線的阻抗匹配,以防止信號(hào)反射和損耗。使用適當(dāng)?shù)膶挾群烷g距,或者添加阻抗匹配的網(wǎng)絡(luò)。

6. 信號(hào)走線方向: 盡量避免信號(hào)線的急轉(zhuǎn)彎和直角,這樣可以減小信號(hào)的輻射和損耗。使用45度角或曲線,盡量保持走線平滑。

7. 高頻信號(hào)走線: 對(duì)于高頻信號(hào),要盡可能短、直接地連接到相應(yīng)的元件。減小走線長度可以降低傳輸線上的信號(hào)損耗。

8. 電源分布: 電源線應(yīng)該足夠?qū)捯越档碗娮瑁乙苊夂兔舾行盘?hào)線平行走線,以減小電磁干擾。

9. 繞過電容: 在電源線附近放置繞過電容,以減小電源噪聲傳播到其他部分的可能性。

10. 測試點(diǎn): 在需要測試的關(guān)鍵點(diǎn)上添加測試點(diǎn),以便在調(diào)試和維護(hù)過程中更容易診斷問題。

11. 距離規(guī)劃: 避免將高頻和低頻信號(hào)線靠得太近,以減小互相之間的干擾。

12. 規(guī)避敏感區(qū)域: 盡量避免將信號(hào)線穿越敏感元件、射頻(RF)區(qū)域或模擬/數(shù)字轉(zhuǎn)換器(ADC/DAC)的附近。

13. 參考設(shè)計(jì)規(guī)范: 遵循 PCB 廠商的設(shè)計(jì)規(guī)范,特別是有關(guān)最小走線寬度、間距、最小孔徑等方面的要求。

14. 使用 EDA 工具: 利用電子設(shè)計(jì)自動(dòng)化(EDA)工具進(jìn)行布線,這些工具可以幫助進(jìn)行規(guī)則檢查、仿真和優(yōu)化。

15. 熱管理: 對(duì)于高功率元件,要考慮散熱問題,確保有足夠的散熱電流路徑和散熱器。

以上這些技巧是通用的,具體的情況可能需要根據(jù)項(xiàng)目的要求和PCB的特殊性進(jìn)行調(diào)整。在PCB設(shè)計(jì)中,不斷的實(shí)踐和經(jīng)驗(yàn)積累也是非常重要的。

獲取報(bào)價(jià)