導(dǎo)航

微信

頂部

news center

發(fā)布時(shí)間:2025-07-10 閱讀: 來源:管理員

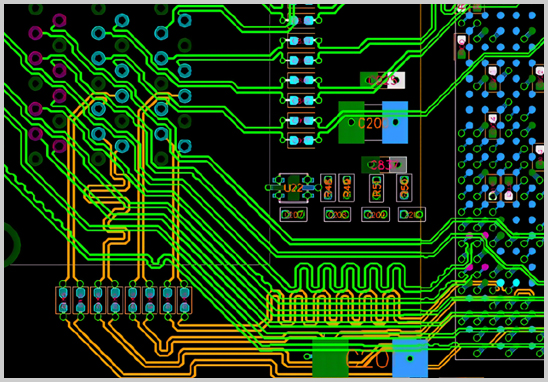

在PCB設(shè)計(jì)過程中,遵循一些經(jīng)過驗(yàn)證的“黃金法則”能大幅提升板子的性能、可制造性和可靠性。下面結(jié)合行業(yè)經(jīng)驗(yàn)與標(biāo)準(zhǔn),分享10條必備的PCB設(shè)計(jì)法則,并提供相關(guān)出處供參考,助您打造高品質(zhì)多層、高精密/BGA封裝及盲孔/埋孔PCB。

1. 選擇合適的網(wǎng)格(Grid Selection)

始終使用與大多數(shù)元件封裝匹配的網(wǎng)格間距,可避免后期布線時(shí)產(chǎn)生“無網(wǎng)格可用”的尷尬。建議初期設(shè)置0.5?mm或0.635?mm(25?mil)為通用網(wǎng)格;對(duì)BGA或HDI板,可輔以0.25?mm(10?mil)細(xì)網(wǎng)格。

2. 科學(xué)的元件布局(Component Placement)

“先大后小,先難后易”是元件布局的不二法則:優(yōu)先放置時(shí)鐘振蕩器、高速接口和散熱器件,再布置被動(dòng)元件與連接器。布局時(shí)要考慮信號(hào)流向,模擬與數(shù)字、電源與地要分區(qū)布局,減少相互干擾。

3. 最短走線原則(Shortest Path)

走線越短,串?dāng)_、阻抗和時(shí)延就越小。尤其是時(shí)鐘、差分對(duì)和高速總線等關(guān)鍵路徑,應(yīng)盡量縮短走線并保證等長(zhǎng)。短走線還能降低寄生電抗,提升信號(hào)完整性。

4. 合理的線寬與線距(Trace Width & Spacing)

根據(jù)信號(hào)電流大小與阻抗要求選取線寬:一般信號(hào)線8–10?mil,1?A電源線40?mil以上;控制線距至少為線寬的2倍,以防止串?dāng)_與短路。此外,高速差分線要滿足特征阻抗設(shè)計(jì),如50?Ω或100?Ω差分。

5. 完整的電源與地平面(Power & Ground Planes)

在多層板中,盡量將一整層做為地平面,再將相鄰層設(shè)為電源平面。這種疊層結(jié)構(gòu)可形成穩(wěn)定低阻抗的回流路徑,減少EMI并提高散熱性能。四層板常見的堆棧順序?yàn)椋翰考莹C地–電源–走線層。

6. 避免直角走線(Avoid 90° Angles)

90°銳角或直角走線會(huì)引起蝕刻誤差并形成不均勻阻抗,高速信號(hào)還易產(chǎn)生反射。推薦使用45°斜角走線或圓弧走線,以保證信號(hào)平滑過渡并提高制造良率。

7. 合理使用過孔(Via Usage)

過孔會(huì)增加寄生電感與阻抗,影響高速信號(hào)完整性。多層板中應(yīng)將過孔數(shù)量控制在最低,并在關(guān)鍵差分對(duì)與高頻線避開過孔;必要時(shí)可使用盲孔、埋孔或微通孔(microvia)來優(yōu)化HDI板設(shè)計(jì)。

8. 仔細(xì)考慮EMC/信號(hào)完整性(EMC & Signal Integrity)

保持電源與地平面連貫,避免平面分割;在敏感高速信號(hào)旁設(shè)置過孔屏蔽或“via fence”防止輻射泄漏;關(guān)鍵路徑加入差分對(duì)與阻抗控制,必要時(shí)做仿真校驗(yàn)。

9. 面向可制造性與裝配(DFM & DFA)

在設(shè)計(jì)前要閱讀目標(biāo)工廠的設(shè)計(jì)規(guī)則(DRC),確保最小焊盤尺寸、絲印間距、SMT貼裝方向等符合廠商可加工范圍;同時(shí)留出調(diào)試與維修空間,避免貼裝后無法測(cè)試或返修。遵循“可測(cè)可裝”原則,可降低后期成本與風(fēng)險(xiǎn)。

10. 嚴(yán)謹(jǐn)?shù)陌鎴D校驗(yàn)與仿真(Design Rule Check & Simulation)

完成布局布線后,務(wù)必執(zhí)行DRC、ERC和電氣規(guī)則檢查;針對(duì)高速通道與電源完整性進(jìn)行SI/PI仿真(如時(shí)域反射、電壓跌落分析),提前發(fā)現(xiàn)潛在問題,避免試板返工。

以上10條黃金法則涵蓋了從基礎(chǔ)布局到高級(jí)信號(hào)完整性與EMC的關(guān)鍵步驟。無論您是新手還是資深工程師,遵循這些守則,都能顯著提升PCB質(zhì)量與可靠性。深圳宏力捷電子專注多層、高精密/BGA和HDI板設(shè)計(jì)服務(wù),從原理圖到樣板交付,全程協(xié)助。

獲取報(bào)價(jià)